# ECMA EUROPEAN COMPUTER MANUFACTURERS ASSOCIATION

# **STANDARD ECMA-103**

PHYSICAL LAYER AT THE BASIC ACCESS INTERFACE BETWEEN DATA PROCESSING EQUIPMENT AND PRIVATE SWITCHING NETWORKS

Free copies of this document are available from ECMA,

European Computer Manufacturers Association

114 Rue du Rhône – 1204 Geneva (Switzerland)

# ECMA EUROPEAN COMPUTER MANUFACTURERS ASSOCIATION

## **STANDARD ECMA-103**

PHYSICAL LAYER AT THE

BASIC ACCESS INTERFACE

BETWEEN DATA PROCESSING

EQUIPMENT AND PRIVATE

SWITCHING NETWORKS

## BRIEF HISTORY

This Standard ECMA-103 is one of a series of standards for the connection of data processing equipment to private switching networks.

It uses the ISDN concepts as developed by CCITT and it is also within the framework of standards for open systems interconnection as defined by ISO 7498 and within the Technical Report ECMA TR/24. It is based on the practical experience of ECMA member companies and the results of their active and continuous participation in the work of ISO, CCITT and various national standardization bodies in Europe and in the USA. It represents a pragmatic and widely based consensus.

The Standard ECMA-103 defines the Physical Layer of the interface as presented by the data processing equipment. Where appropriate, assumptions on the interface as presented by the private circuit switching network are also indicated.

The second edition has been adapted to CCITT Rec. I.430 as approved by the Accelerated Procedure in 1987.

Accepted as Standard ECMA-103, 2nd Edition, by the General Assembly of ECMA of 10th December 1987.

## TABLE OF CONTENTS

|    |                                                                                                                                                                                                                                                                                                                                                                                                           | Pages                                                    |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 1. | SCOPE AND FIELD OF APPLICATION                                                                                                                                                                                                                                                                                                                                                                            | 1                                                        |

| 2. | REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                        |

| 3. | DEFINITIONS                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                        |

|    | <ul> <li>3.1 B-Channel</li> <li>3.2 D-Channel</li> <li>3.3 Data Processing Equipment (DPE)</li> <li>3.4 Interworking Unit (IWU)</li> <li>3.5 Layer Service</li> <li>3.6 Private Switching Network (PSN)</li> <li>3.7 PSN Termination (PT)</li> <li>3.8 S0 Interface</li> <li>3.9 S2 Interface</li> <li>3.10 Specification and Description Language (SDL)</li> <li>3.11 Terminal Equipment (TE)</li> </ul> | 2<br>2<br>2<br>2<br>2<br>3<br>3<br>3<br>3<br>3<br>3<br>3 |

| 4. | LAYER SERVICE CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                             | 3                                                        |

|    | <ul> <li>4.1 Layer Services required from the Physical Medium</li> <li>4.2 Layer Services provided to the Data Link Layer</li> <li>4.3 Primitives between the Physical Layer and other Entities</li> </ul>                                                                                                                                                                                                | 3<br>3<br>4                                              |

| 5. | MODES OF OPERATION                                                                                                                                                                                                                                                                                                                                                                                        | 5                                                        |

|    | <ul><li>5.1 Point-to-Point Operation</li><li>5.2 Point-to-Multipoint Operation</li></ul>                                                                                                                                                                                                                                                                                                                  | 5<br>5                                                   |

| 6. | TYPES OF WIRING CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                             | 6                                                        |

|    | <ul> <li>6.1 Point-to-Point Configuration</li> <li>6.2 Point-to-Multipoint Configuration</li> <li>6.3 Wiring Polarity Integrity</li> <li>6.4 Location of the Interfaces</li> <li>6.5 DPE associated Wiring</li> </ul>                                                                                                                                                                                     | 6<br>6<br>6<br>7<br>7                                    |

| 7. | FUNCTIONAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                | 7                                                        |

|    | 7.1 Interface Functions                                                                                                                                                                                                                                                                                                                                                                                   | 7                                                        |

|    | <ul> <li>7.1.1 Bit Timing</li> <li>7.1.2 Octet Timing</li> <li>7.1.3 Frame Alignment</li> <li>7.1.4 B-Channel</li> <li>7.1.5 D-Channel</li> <li>7.1.6 D-Channel Access Procedure</li> <li>7.1.7 Power Feeding</li> </ul>                                                                                                                                                                                  | 7<br>8<br>8<br>8<br>8<br>8                               |

|    |                   | 7.1.8<br>7.1.9                   | Deactivation Activation                                                                                                                                                                     | 8                                |

|----|-------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|    | 7.2<br>7.3<br>7.4 | Conn                             | hange Circuits<br>ected/Disconnected Indication<br>e Structure                                                                                                                              | 8<br>8<br>9                      |

|    |                   | 7.4.1<br>7.4.2                   | Bit Rate Binary Organization of the Frame                                                                                                                                                   | 9<br>9                           |

|    | 7.5<br>7.6        | Line (                           | Code<br>ng Considerations                                                                                                                                                                   | 12<br>12                         |

| 8. | INT               | ERFA                             | CE PROCEDURES                                                                                                                                                                               | 13                               |

|    | 8.1               | D-Ch                             | annel Access Procedure                                                                                                                                                                      | 13                               |

|    |                   | 8.1.2<br>8.1.3<br>8.1.4<br>8.1.5 | Interframe Time Fill D-Echo Channel D-Channel Monitoring Priority Mechanism Collision Detection Access Control Procedure                                                                    | 13<br>13<br>13<br>13<br>14<br>14 |

|    | 8.2               | Activ                            | ation/Deactivation                                                                                                                                                                          | 16                               |

|    |                   | 8.2.2<br>8.2.3                   | Definitions Activation/Deactivation Procedure at the Terminal Side Activation/Deactivation Procedure at the PSN Side SDL Presentation of the Activation/Deactivation Procedur Timing Values | 16<br>19<br>22<br>e24<br>30      |

|    | 8.3               | Fram                             | e Alignment Procedure                                                                                                                                                                       | 31                               |

|    |                   | 8.3.1<br>8.3.2                   | Frame Alignment Procedure in the Direction PT to DPE Frame Alignment in the Direction DPE to PT                                                                                             | 32<br>32                         |

|    | 8.4<br>8.5        |                                  | Channel Code on B-Channels framing                                                                                                                                                          | 32<br>32                         |

|    |                   | 8.5.2<br>8.5.3                   | Q-Bit Identification Multiframe Identification Q-Bit Position Identification Algorithm Multiframe Identification by the DPE                                                                 | 32<br>33<br>33<br>34             |

| 9. | PRO               | OVISIO                           | ONS FOR PHYSICAL LAYER MAINTENANCE                                                                                                                                                          | 34                               |

|    | 9.1<br>9.2<br>9.3 | Mana                             | Loopback<br>Igement Entity Primitives<br>Bit Stream                                                                                                                                         | 34<br>35<br>36                   |

|    |                   | 9.3.1<br>9.3.2                   | Continuous ZEROs<br>Isolated ZEROs                                                                                                                                                          | 36<br>36                         |

|    | 9.4               | D-Ec                             | ho-Bit                                                                                                                                                                                      | 36                               |

| 10. | ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                             | 36                         |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

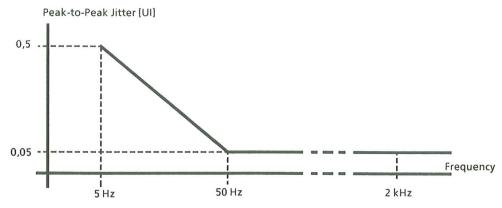

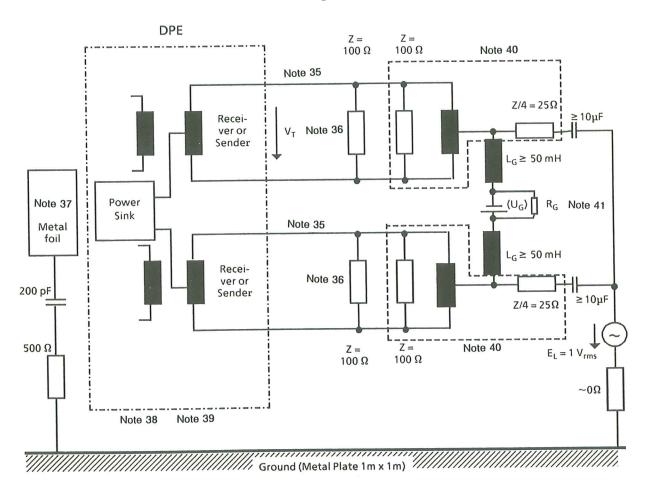

|     | 10.1 Bit Rate<br>10.2 Jitter and Bit Rate Relationship between DPE Input and Output                                                                                                                                                                    | 36<br>37                   |

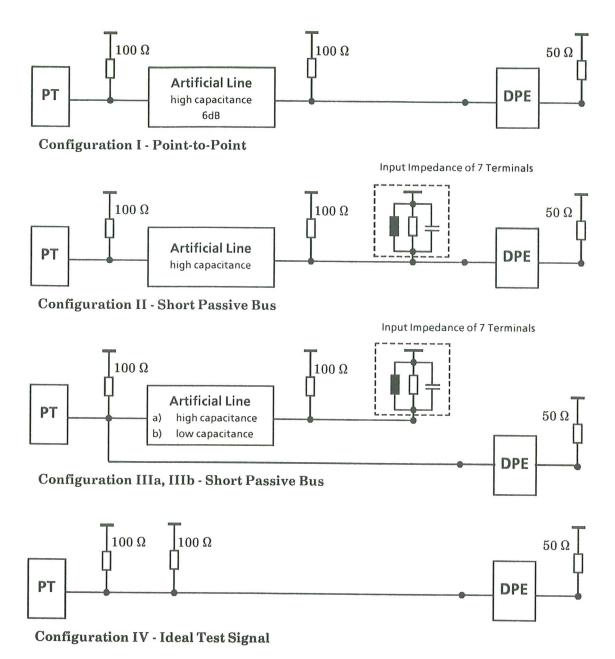

|     | <ul><li>10.2.1 Test Configuration</li><li>10.2.2 Timing Extraction Jitter</li><li>10.2.3 Total Phase Deviation</li></ul>                                                                                                                               | 37<br>41<br>41             |

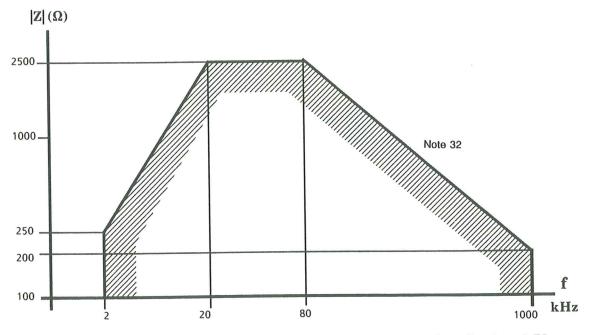

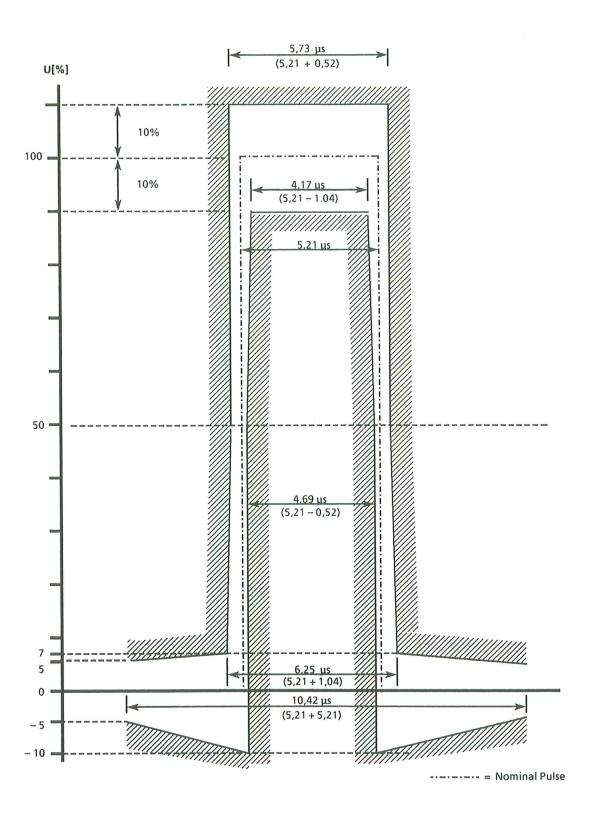

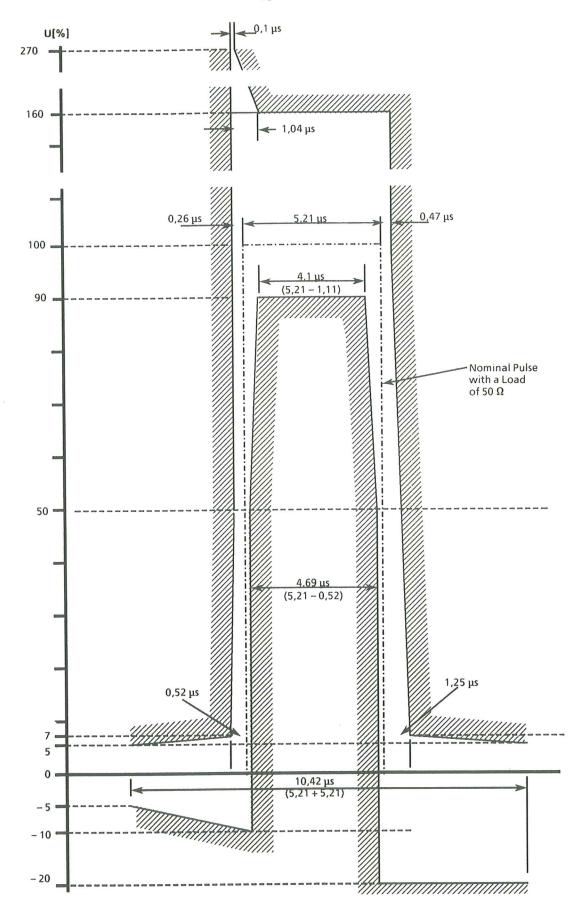

|     | <ul><li>10.3 PT Jitter Characteristics</li><li>10.4 Termination of the Line</li><li>10.5 DPE Output Characteristics</li></ul>                                                                                                                          | 42<br>42<br>43             |

|     | <ul> <li>10.5.1 DPE Output Impedance</li> <li>10.5.2 Test Load Impedance</li> <li>10.5.3 Pulse Shape and amplitude (ZERO)</li> <li>10.5.4 Pulse Unbalance</li> <li>10.5.5 Voltage on Other Test Loads</li> <li>10.5.6 Unbalance about Earth</li> </ul> | 43<br>44<br>44<br>44<br>47 |

|     | 10.6 DPE Input Characteristics                                                                                                                                                                                                                         | 50                         |

|     | <ul><li>10.6.1 DPE Receiver Input Impedance</li><li>10.6.2 Receiver Sensitivity, Noise and Distortion Immunity</li><li>10.6.3 Unbalance about Earth</li></ul>                                                                                          | 50<br>50<br>51             |

|     | <ul><li>10.7 Isolation from external Voltages</li><li>10.8 Interconnecting Media Characteristics</li><li>10.9 Standard ISDN Basic Access TE Cord</li></ul>                                                                                             | 51<br>51<br>51             |

|     | 10.9.1 Cords with a maximum Length of 7 m 10.9.2 Cords having a Length greater than 7 m                                                                                                                                                                | 51<br>51                   |

|     | 10.10 Cords forming Part of the DPE                                                                                                                                                                                                                    | 51                         |

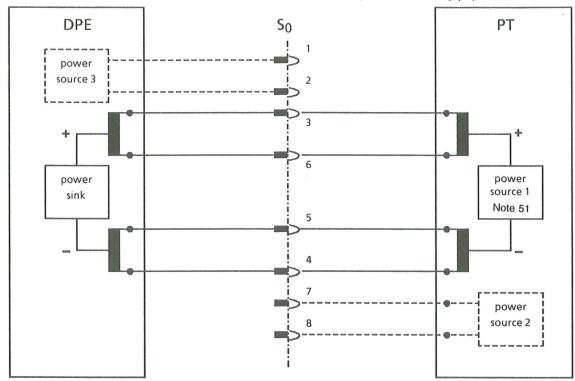

| 11. | POWER FEEDING                                                                                                                                                                                                                                          | 52                         |

|     | 11.1 Reference Configuration                                                                                                                                                                                                                           | 52                         |

|     | <ul><li>11.1.1 Functions Specified for the Access Leads</li><li>11.1.2 Provision of Power Sources</li></ul>                                                                                                                                            | 52<br>52                   |

|     | <ul><li>11.2 Power available at the DPE from Power Source 1</li><li>11.3 Power Source 1 Consumption</li></ul>                                                                                                                                          | 53<br>53                   |

|     | <ul><li>11.3.1 Normal Power Conditions</li><li>11.3.2 Restricted Power Conditions</li></ul>                                                                                                                                                            | 53<br>54                   |

|     | 11.4 Current transients                                                                                                                                                                                                                                | 54                         |

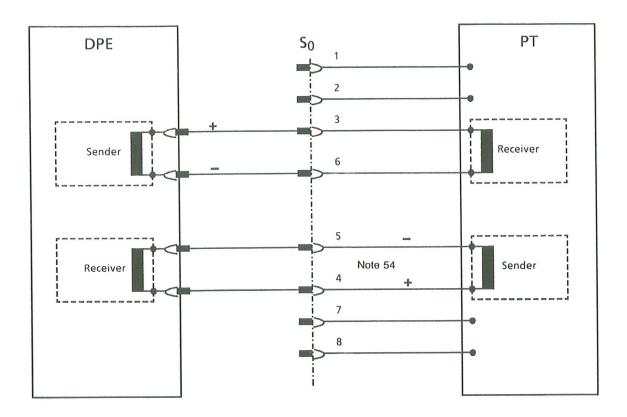

| 12. | PHYSICAL CHARACTERISTICS                                                                                                                                                                                                                               | 54                         |

|     | 12.1 Connectors 12.2 Connection Cord                                                                                                                                                                                                                   | 54<br>54                   |

|     | 12.2.1 Use of the Access Leads 12.2.2 Signal Polarity of the Access Leads                                                                                                                                                                              | 54<br>55                   |

## 1. SCOPE AND FIELD OF APPLICATION

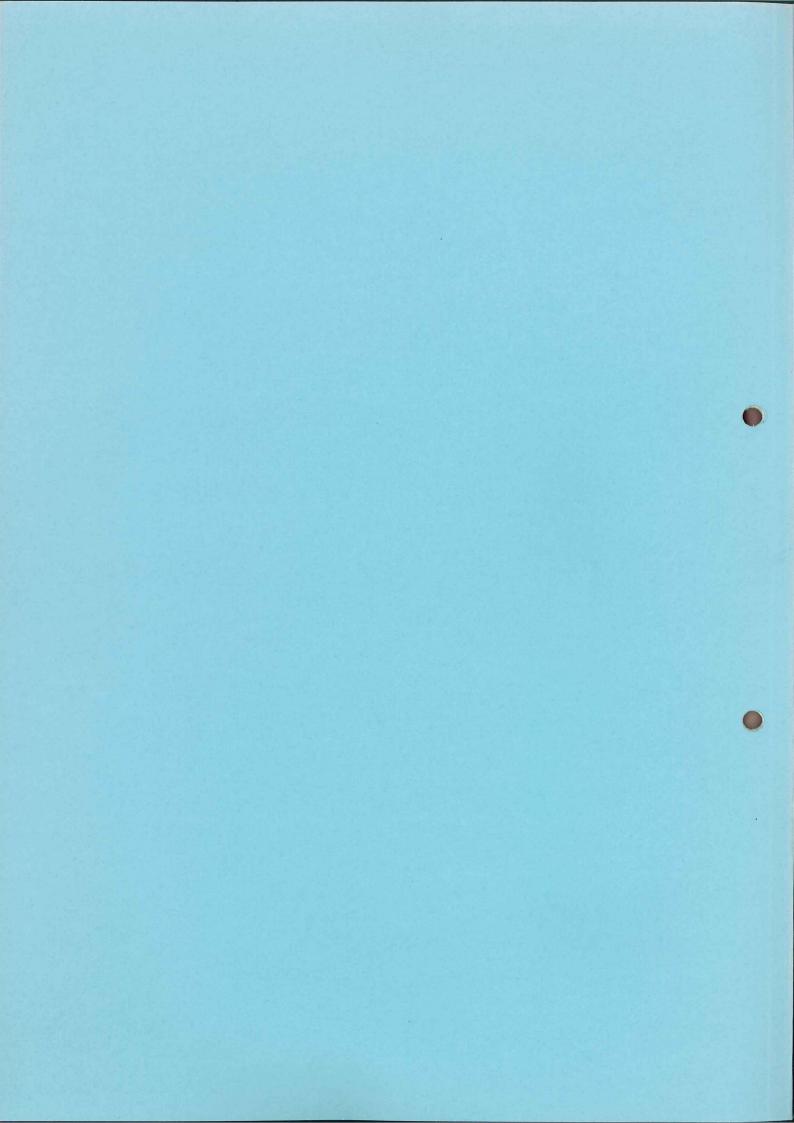

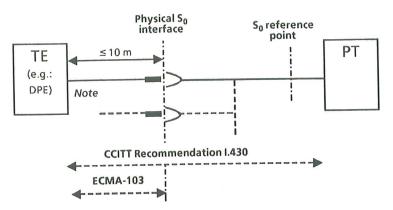

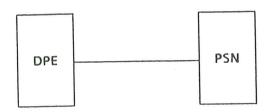

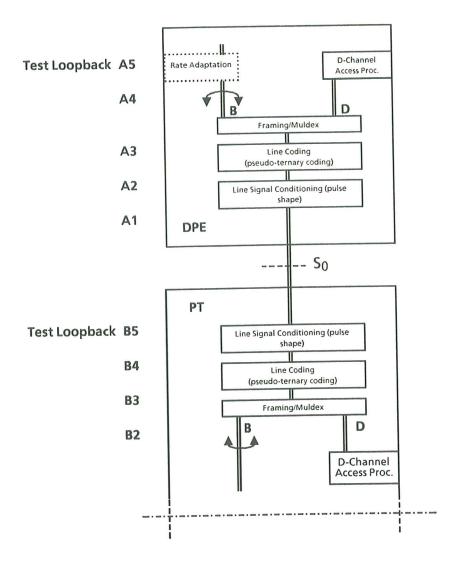

This ECMA Standard specifies the Physical Layer characteristics of the basic access interface between data processing equipment (DPE) and private switching networks (PSN), and is based on CCITT Rec. I.430. The interface concerned is at the S reference point as defined in CCITT Rec. I.411. The reference configuration for the interface is given in Figure 1.

Figure 1 - Reference Configuration showing  $\boldsymbol{S}_0$  and  $\boldsymbol{S}_2$  Interfaces

## 2. REFERENCES

| ECMA-83          | Safety Requirements for DTE-to-DCE Interface in Public Data Networks                         |

|------------------|----------------------------------------------------------------------------------------------|

| ECMA-105         | Data Link Layer Protocol between Data Processing<br>Equipment and Private Switching Networks |

| ECMA TR/35       | Safety Requirements for Equipment to be connected to Telecommunication Networks              |

| CCITT Rec. G.117 | Transmission aspects of unbalance about earth (definitions and method)                       |

| CCITT Rec. I.112 | Vocabulary of terms for ISDNs                                                                |

| CCITT Rec. I.320 | ISDN protocol reference model                                                                |

| CCITT Rec. I.411 | ISDN user-network interfaces - reference configurations                                      |

| CCITT Rec. I.412 | ISDN user-network interfaces - interface structures and access capabilities                  |

| CCITT Rec. I.430 | Basic user-network interface - layer 1 specification                                         |

| CCITT Rec. O.121 | Measuring arrangements to assess the degree of unbalance about earth                         |

| CCITT Rec. V.52     | Characteristics of distortion and error-rate measuring apparatus for data transmission    |

|---------------------|-------------------------------------------------------------------------------------------|

| CCITT Rec. V.57     | Comprehensive data test set for high data signalling rates                                |

| CCITT Rec. X.200    | Reference model of Open Systems Interconnection for CCITT applications                    |

| CCITT Rec. X.211    | Physical layer service definitions of open system interconnections for CCITT applications |

| CCITT Rec. Z.101104 | Recommendations on the functional specification and description language (SDL)            |

## Note 1

For the CCITT Recommendations listed above (except 1.430) the Red Book versions apply. The reference for CCITT Rec. 1.430 can be found in report COM. XVIII R21 C.

| ISO 7498                   | Open Systems Interconnection - Basic Reference<br>Model                                                                                        |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| I <mark>SO</mark> DIS 8877 | Information Processing Systems-Interface connector and contact assignment for ISDN basic access interface located at reference points S and T. |

## 3. DEFINITIONS

A basic vocabulary of terms can be found in CCITT Rec. I.112. In addition, the following definitions apply in this Standard:

## 3.1 B-Channel

A 64 kbit/s access channel with bit and octet timing used to carry user data in both directions of transmission between DPEs connected over a PSN.

## 3.2 D-Channel

A 16 kbit/s access channel used to carry signalling and other information in both directions of transmission between a DPE and the PSN.

## 3.3 Data Processing Equipment (DPE)

Specific type of terminal equipment, exclusively or mainly used to process data (in contrast to a voice-only terminal).

## 3.4 Interworking Unit (IWU)

The functional block needed for a PSN to interwork with other networks.

## 3.5 Layer Service

This term is defined in the ISO Reference Model on Open Systems Interconnections (ISO 7498).

## 3.6 Private Switching Network (PSN)

A private ISDN providing circuit and/or packet/frame switching functions. It is operated by the user and located on his premises to cover the communications needs in his domain. Data processing equipment is connected to a PCSN at its S reference points.

## 3.7 PSN Termination (PT)

The termination of a PSN at the S reference point.

## 3.8 S<sub>0</sub> Interface

The basic access interface at the S reference point (see CCITT Rec. I.411) operating at a physical bit rate of 192 kbit/s. It provides access to two B-channels and one D-channel (2B + D). The  $S_0$  interface forms one of the user access points to a PSN.

## 3.9 S<sub>2</sub> Interface

The primary rate access interface at the S reference point (see CCITT Rec. I.411) operating at a physical bit rate of 2048 kbit/s. It provides access to 30 B-channels and one D-channel (30B + D). The  $S_2$  interface forms one of the user access points to a PSN.

## 3.10 Specification and Description Language (SDL)

The specification and description language according to CCITT Rec. Z.101 to Z.104.

## 3.11 Terminal Equipment (TE)

A general term to designate any terminal (voice or data processing or combination of both) connected to a PSN at the  $S_0$  or at the  $S_2$  interface.

## 4. LAYER SERVICE CHARACTERISTICS

General information on layer services and layered protocols can be found in CCITT Rec. X.200 and ISO 7498.

## 4.1 Layer Services required from the Physical Medium

The Physical Layer of this interface requires a balanced metallic transmission medium for each direction of transmission, capable of supporting 192 kbit/s.

## 4.2 Layer Services provided to the Data Link Layer

The Physical Layer shall provide the following layer services to the Data Link Layer:

- Transmission capability by means of appropriately encoded bitstreams, for both B-channels and the D-channel.

- Timing and synchronization functions.

- The signalling capability and the necessary procedures to enable user terminals and/or network terminating equipment to be activated and deactivated. The activation and deactivation procedures are defined in 8.2.

- The signalling capability and the necessary procedures to allow terminals to gain access to the common resource of the D-channel in an orderly fashion, while meeting the performance requirements of the D-channel signalling systems. These D-channel access control procedures are defined in 8.1.

- The signalling capability and procedures and the necessary functions to enable the maintenance functions to be performed.

- An indication to the higher layers and the Management Entity about the status of the Physical Layer.

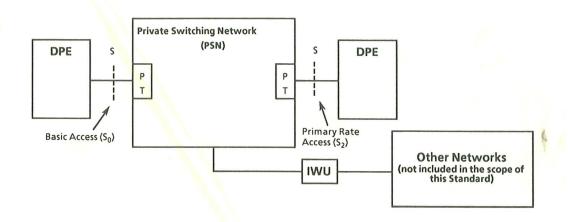

## 4.3 Primitives between the Physical Layer and other Entities

- The primitives used between the Physical Layer and other entities are:

| PH-AI/AR, MPH-AI/AR | see 8.2.1.4                                |

|---------------------|--------------------------------------------|

| PH-DI, MPH-DI/DR    | see 8.2.1.5                                |

| MPH-EI/ES           | see 8.2.1.6                                |

| MPH-II              | see 8.2.1.7                                |

| PH-DATA-I/R         | PHYSICAL LAYER DATA INDICATION/<br>REQUEST |

These primitives are used to indicate the arrival of a message unit or to request that a message unit be sent.

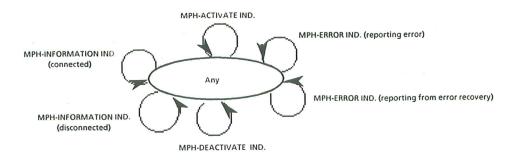

- The primitives represent the logical exchange of information and control between the Physical Layer, the Data Link Layer and the Management Entity, see Figure 2. They do not specify nor constrain the implementation of entities or interfaces. For a description of the syntax and use of the primitives refer to CCITT Rec. X.211.

Figure 2 - Physical Layer Primitives

- The values of the primitives are defined in Table 1. Relevant detailed description of the primitives and their procedures are given in 8.2.1.

|                 | Function                |                 | Parameter                |                 | Message Unit                            |                            |

|-----------------|-------------------------|-----------------|--------------------------|-----------------|-----------------------------------------|----------------------------|

| Generic Name    | Request                 | Indica-<br>tion | Priority<br>Indicator    | Message<br>Unit | Contents                                |                            |

| PH-DATA         | x<br>Note 2             | х               | x<br>Note 3              | х               | Data Link Layer<br>peer-to-peer message | tetween Phy-sical and      |

| PH-ACTIVATE     | х                       | х               | -                        | -               |                                         | Data Link Layer            |

| PH-DEACTIVATE   | 1005                    | х               | -                        | -               |                                         | <b> </b>                   |

| MPH-ACTIVATE    | х                       | х               | -                        |                 |                                         | 1                          |

| MPH-DEACTIVATE  | х                       | Х               | -                        | х               |                                         | between Physical Layer and |

| MPH-ERROR       | -                       | x<br>Note 4     | -                        | х               | Note 4                                  | Management Entity<br>↓     |

| MPH-INFORMATION | IPH-INFORMATION - x - x |                 | Connected / Disconnected |                 |                                         |                            |

Table 1 - Values of Physical Layer Primitives

#### Note 2

PH-DATA-REQUEST implies underlying negotiation between the Physical and the Data Link Layer for the acceptance of the data.

#### Note 3

Priority indication applies only to the REQUEST type.

#### Note 4

The indication includes the type of error or recovery from a previously reported erroneous situation.

#### 5. MODES OF OPERATION

The characteristics of the Physical Layer interface shall allow for point-to-point and point-to-multipoint modes of operation. The mode of operation used at the Physical Layer shall not affect the procedures at higher layers.

## 5.1 Point-to-Point Operation

Point-to-point operation at the Physical Layer shall imply that only one source (sender) and one sink (receiver) are active at the interface at any one time in each direction of transmission. Such operation shall be independent of the number of connectors which may be provided on a particular wiring configuration (see 6).

## 5.2 Point-to-Multipoint Operation

Point-to-multipoint operation at the Physical Layer shall allow more than one terminal (source and sink pair) to be simultaneously active at an S reference point. The multipoint mode of operation may be accommodated, as discussed in 6, with point-to-point or point-to-multipoint wiring configurations.

#### 6. TYPES OF WIRING CONFIGURATION

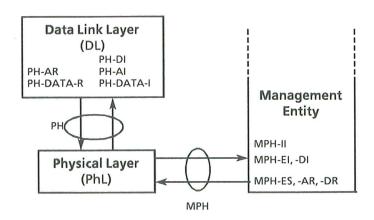

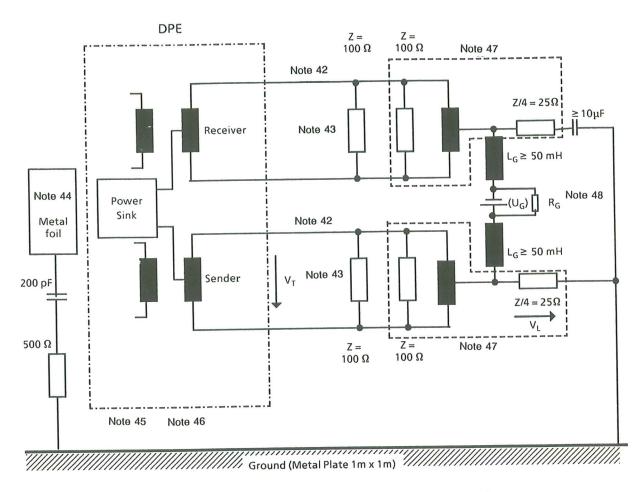

Figure 3 shows general reference configurations for the wiring at user premises. The electrical characteristics of the  $S_0$  interface are determined on the basis of certain assumptions about the various wiring configurations which may exist within users' premises. These assumptions are identified in the configuration descriptions of Figure 3.

## 6.1 Point-to-Point Configuration

Point-to-point wiring configuration shall imply that only one source (sender) and one sink (receiver) are interconnected via an interchange circuit.

## **6.2** Point-to-Multipoint Configuration

Point-to-multipoint wiring configurations shall allow more than one source to be connected to the same sink or more than one sink to be connected to the same source via an interchange circuit. Such distribution systems are called "passive busses" and are characterized by the fact that they contain no active logic elements.

Figure 3 - Reference Configurations for Basic Access Wiring at the User's Premises

## Note 5

The lengths depend on the electrical characteristics of the cabling and the values indicated are given for tutorial background information only.

## 6.3 Wiring Polarity Integrity

For a point-to-point wiring configuration the two wires of the interchange circuit pair may be reversed. However for point-to-multipoint wiring configurations, the

wiring polarity integrity of the interchange circuit from the TEs to the PT shall be maintained between the TEs.

## 6.4 Location of the Interfaces

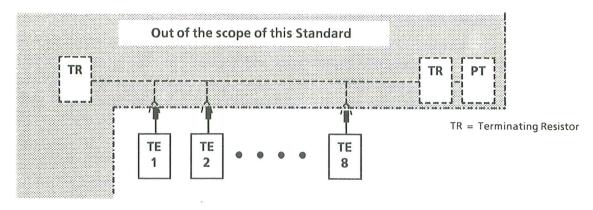

The wiring on the user's premises shall be considered to be one continuous cable run with sockets for the TE attached directly to the cable or using stubs of shorter than 1 m. The socket and the wiring on the user's premises are beyond the scope of this Standard, see Figure 4.

Figure 4 - Location of the S<sub>0</sub> Interface

#### Note 6

The connection cord may be detachable.

## 6.5 DPE associated Wiring

The wiring between DPE and its associate socket can affect the electrical characteristics of the interface. A DPE may be equipped with either of the following means for connection to the interface point:

- a hard-wired connection cord of not more than 10 m and a connector as specified in 12.1, or

- a socket with a connection cord of not more than 10 m, which has a connector as specified in 12.1, at each end.

Although a DPE may be provided with a cord of less than 5 m, it shall meet the requirements of this Standard with a cord having a minimum length of 5 m. Such a cord may be provided as part of the DPE, or the DPE may be designed to conform to the electrical characteristics specified in 10 with a "standard ISDN basic access TE cord" conforming to the requirements specified in 10.9 and having the maximum permitted capacitance.

## 7. FUNCTIONAL CHARACTERISTICS

## 7.1 Interface Functions

#### 7.1.1 Bit Timing

This function shall provide bit (signal element) timing at 192 kbit/s to enable DPE and PT to recover information from the aggregate bit stream.

## 7.1.2 Octet Timing

This function shall provide 8 kHz octet timing for the PT and DPE.

## 7.1.3 Frame Alignment

This function shall provide information to enable PT and DPE to recover the time division multiplexed channels.

## 7.1.4 B-Channel

This function shall provide two independent access channels each having a bit rate of 64 kbit/s for each direction of transmission, as defined in CCITT Rec. I.412.

## 7.1.5 D-Channel

This function shall provide an access channel with a bit rate of 16 kbit/s for each direction of transmission, as defined in CCITT Rec. I.412.

## 7.1.6 D-Channel Access Procedure

This function shall enable terminals to gain access to the common resource of the D-channel in an orderly controlled fashion. The functions necessary for these procedures shall include an echoed D-channel at a bit rate 16 kbit/s in the direction PT to DPE. For the definition of the procedures relating to D-channel access, see 8.1.

## 7.1.7 Power Feeding

This function shall provide for the capability to transfer power across the interface from the PSN (PT) to the DPE. The detailed specification of the power feeding function is given in 11.

## 7.1.8 Deactivation

This function shall permit the DPE to be placed in a lower power consumption mode, e.g. when no call is in progress. The procedures and precise conditions under which deactivation takes place are specified in 8.2.

## 7.1.9 Activation

This function shall allow DPE and PT to be restored to their normal operating power mode. The procedures and precise conditions under which such deactivation takes place are specified in 8.2.

## 7.2 Interchange Circuits

Two interchange circuits, one for each direction of transmission, shall be used to transfer digital signals across the interface. All functions described in 7.1, except for power feeding, shall be carried by means of a digitally multiplexed signal structured as defined in 7.4.

## 7.3 Connected/Disconnected Indication

The appearance/disappearance of power shall be the criterion used by the DPE to determine whether it is connected/disconnected.

A terminal powered across the interface shall consider itself connected when it detects the presence of power.

A terminal not powered across the interface may consider itself disconnected either if it can detect the disappearance of voltage from power source 1 (when provided; see 11) or on absence of local power.

The indication, that the terminal is disconnected, shall be sent to the Management Entity by means of the MPH-Error Indication primitive.

#### 7.4 Frame Structure

In both directions of transmissions, the bits shall be grouped into frames of 48 bits each. The frame structure shall be identical for point-to-point and point-to-multipoint configurations.

## 7.4.1 Bit Rate

The nominal transmitted bit rate at the interface shall be 192 kbit/s in both directions of transmission.

## 7.4.2 Binary Organization of the Frame

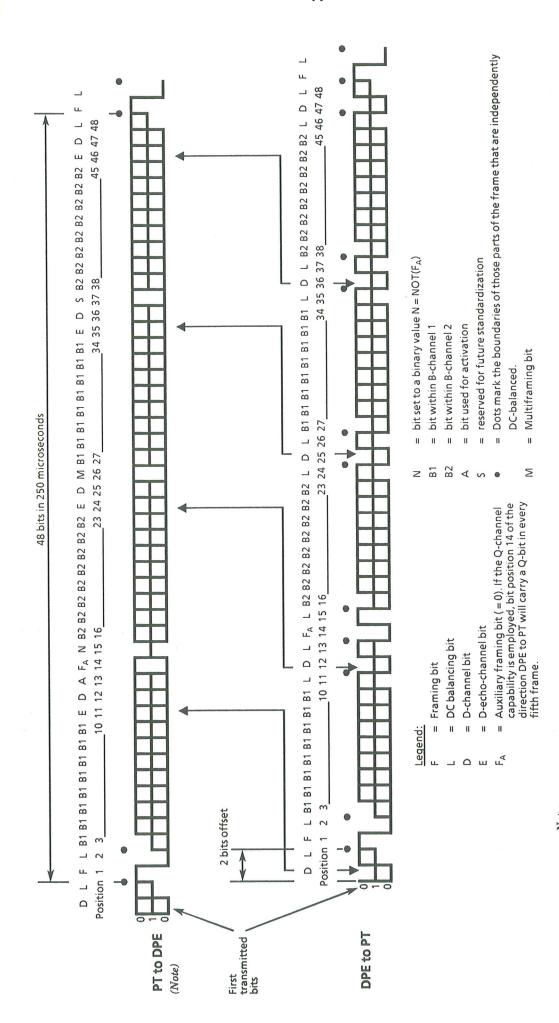

The frame structures are different for each direction of transmission. Both structures are illustrated in Figure 5.

#### 7.4.2.1 **DPE to PSN**

Each frame shall consist of the following groups of bits, each individual group being DC-balanced by a trailing bit (L-bit):

| <b>Bit Position</b> | Group                                                              |

|---------------------|--------------------------------------------------------------------|

| 1 - 2               | F and L-bit (framing and balance bits)                             |

| 3 - 11              | B1-channel with balance bit (first octet)                          |

| 12 - 13             | D and L-bit (D-channel bit with balance bit)                       |

| 14 - 15             | F <sub>A</sub> or Q and L-bit (auxiliary framing and balance bits) |

| 16 - 24             | B2-channel with balance bit (first octet)                          |

| 25 - 26             | D and L-bit (D-channel bit with balance bit)                       |

| 27 - 35             | B1-channel with balance bit (second octet)                         |

| 36 - 37             | D and L-bit (D-channel bit with balance bit)                       |

| 38 - 46             | B2-channel with balance bit (second octet)                         |

| 47 - 48             | D and L-bit (D-channel bit with balance bit)                       |

## 7.4.2.2 PSN to DPE

Frames transmitted by the PSN shall contain a D-echo channel (E-bits) used to re-transmit the D-bits received from the terminals. The D-echo channel shall be used for D-channel access control. The last bit of the frame (L-bit) shall be used for balancing each complete frame. The bits are grouped as follows:

| Bit Position | Group                                       |

|--------------|---------------------------------------------|

| 1 - 2        | F and L-bits (framing and balance bits)     |

| 3 - 10       | B1-channel (first octet)                    |

| 11           | E-bit (D-Echo-channel bit)                  |

| 12           | D-channel bit                               |

| 13           | A-bit used for activation                   |

| 14           | FA-bit (auxiliary framing bit)              |

| 15           | N-bit (coded as defined in Figure 5)        |

| 16 - 23      | B2-channel (first octet)                    |

| 24           | E-bit (D-Echo-channel bit)                  |

| 25           | D-channel bit                               |

| 26           | M-bit (multi-framing bit)                   |

| 27 - 34      | B1-channel (second octet)                   |

| 35           | E-bit (D-Echo-channel bit)                  |

| 36           | D-channel bit                               |

| 37           | S-bit (reserved for future standardization) |

| 38 - 45      | B2-channel (second octet)                   |

| 46           | E-bit (D-Echo-channel bit)                  |

| 47           | D-channel bit                               |

| 48           | L-bit (frame balance bit)                   |

| Note 7       |                                             |

The S-bit shall be always set to ZERO.

$\overline{Note}$ :

Due to possible reversion of the two wire interchange circuit (see 6.3), the bits may be received with opposite polarity.

Figure 5 - Frame Organization

#### Note 8

Due to possible reversion of the two wire interchange circuits (see 6.3), the bits may be received with opposite polarity.

#### 7.4.2.3 Relative Bit Positions

At the terminals, timing in the direction DPE to PT shall be derived from the frames received from the PT.

The first bit of each frame transmitted from a DPE towards the PT shall be offset by two bit periods with respect to the first bit of the frame received from the PT. Figure 5 illustrates the relative bit positions for both transmitted and received frames.

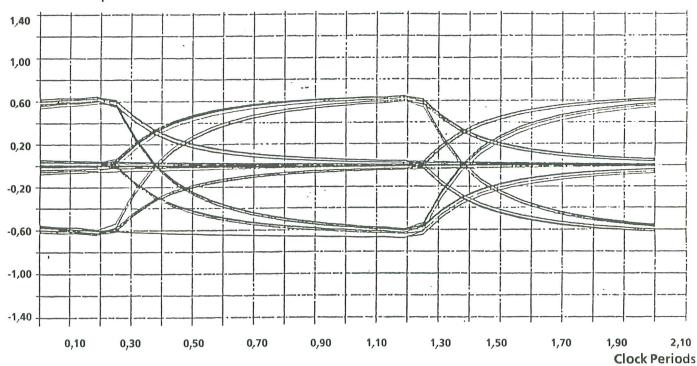

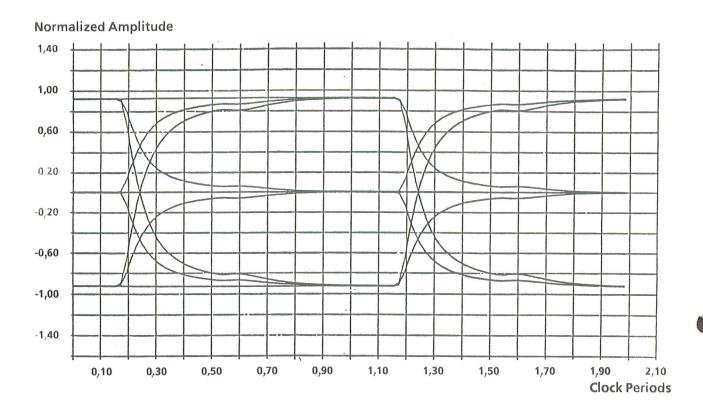

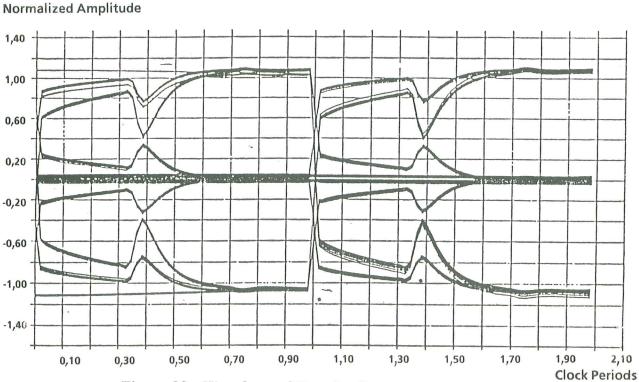

## 7.5 Line Code

For both directions of transmission pseudo-ternary coding is used with 100% pulse width as shown in Figure 6. Coding shall be such that a ONE is represented by no signal voltage applied to the line, and a ZERO is represented by a positive or negative voltage, i.e. a positive or negative pulse. Consecutive ZEROs shall be represented by pulses of opposite voltage.

Figure 6 - Pseudo-Ternary Code (Example)

The framing bit (bit 1, "F") shall always be transmitted as a positive pulse. The balance bit (bit 2, "L") immediately following the framing bit shall be of opposite polarity.

The first ZERO following bit 2 shall be of the same polarity as bit 2. Subsequent ZEROs shall alternate in polarity. A balance bit shall be set to ZERO if the number of ZEROs following the last balance bit is odd. It shall be set to ONE if the number of ZEROs following the last balance bit is even.

## Note 9

Due to possible reversion of the two wire interchange circuits (see 6.3), the bits may be received with opposite polarity.

## 7.6 Timing Considerations

A DPE shall synchronize its timing (bit, octet, frame) to the signal received from the PSN ans use this derived timing to synchronize its transmitted signal.

## 8. INTERFACE PROCEDURES

General information on interface procedures and layered protocols can be found in CCITT Rec. X.200 and Standard ISO 7498. The subsequent paragraphs describe the detailed procedures at the Physical Layer interfaces to the Data Link Layer and to the Management Entity.

## 8.1 D-Channel Access Procedure

The following procedure shall allow a number of terminals, being part of a multipoint configuration, to gain access to the D-channel in an orderly fashion. The procedure shall ensure that, even in cases where two or more terminals attempt to access the D-channel simultaneously, one terminal will always be successful in completing transmission of its information. This procedure relies upon the use of the Data Link Layer frames delimited by flags consisting of the binary pattern 01111110 and the technique of insertion of ZEROs to prevent flag imitation; see Standard ECMA-105.

The D-channel access procedure shall also permit terminals to operate in a point-to-point manner.

#### 8.1.1 Interframe Time Fill

When a DPE or PT has no Data Link Layer frames to transmit, it shall send ONEs on the D-channel.

## 8.1.2 D-Echo Channel

On receipt of a D-channel bit from the DPE(s), the PT shall reflect its binary value in the next available D-echo channel bit position towards the DPE(s).

## 8.1.3 D-Channel Monitoring

In the ACTIVATED state (see 8.2) the DPE shall monitor the D-echo channel and count the number of consecutive ONEs. If a ZERO is detected, the terminal shall restart counting the number of consecutive ONEs. The current value of the count is called C. It need not be incremented after the decimal value 11 has been reached.

## 8.1.4 Priority Mechanism

The Data Link Layer frames shall be transmitted so that signalling information is given priority (priority class 1) over all other types of information (priority class 2). Furthermore, to ensure that within each priority class all competing DPEs are given a fair chance to access the D-channel, once a DPE has successfully completed the transmission of a frame it shall be given a lower level of priority within that class. The terminal is given back its normal level within a priority class when all terminals have had an opportunity to transmit information at the normal level within that priority class.

The priority class shall be passed down from the Data Link Layer as a parameter of the PH-DATA-REQUEST primitive.

The priority mechanism is based on the requirement that a terminal may only start the Data Link Layer frame transmission when C (see 8.1.3) equals, or exceeds, the value  $X_1$  for priority class 1 or equals, or exceeds, the value  $X_2$  for priority class 2. The value  $X_1$  shall be 8 for the normal level and 9 for the lower level of priority. The value  $X_2$  shall be 10 for the normal level and 11 for the lower level of priority.

In either priority class, the value of the normal level of priority shall be changed into the value of the lower level of priority when a terminal has successfully transmitted a Data Link Layer frame of that priority class.

The value of the lower level of priority shall be changed back to the value of the normal level of priority when C (see 8.1.3) equals the value of the lower level of priority.

## 8.1.5 Collision Detection

While transmitting information in the D-channel the terminal shall monitor the received D-echo channel bit and compare the last transmitted bit with the next available D-echo bit. If the transmitted bit is the same as the received echo, the terminal shall continue its transmission. If however, the received echo is different from the transmitted bit the terminal shall cease transmission immediately and return to the D-channel monitoring state.

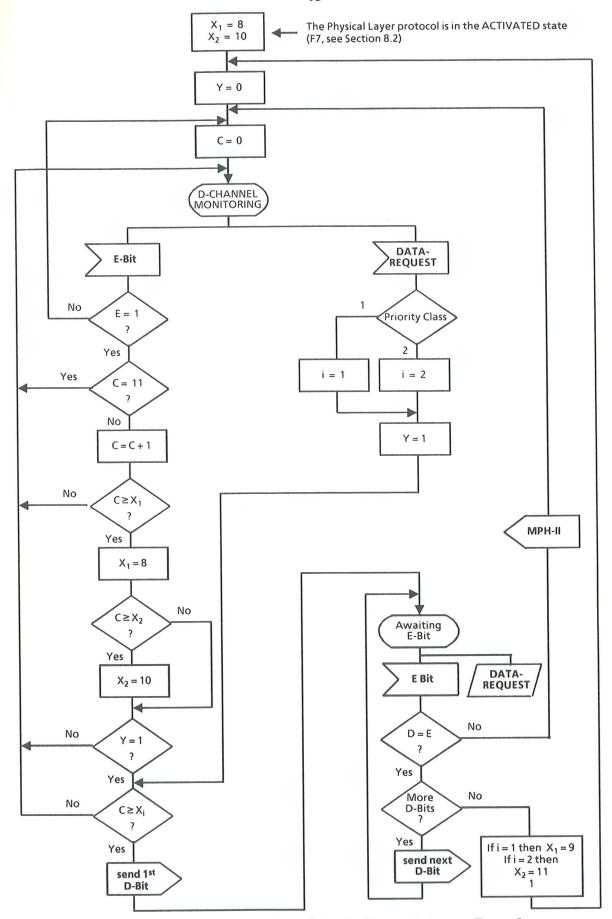

## 8.1.6 Access Control Procedure

Figure 7 shows the SDL diagram of the D-channel access procedure. The following variables are used in the SDL diagram:

C = Count of E-bits received as ONEs

D = Value of the most recently transmitted D-channel bit (D-bit)

i = Priority class of the message to be transmitted (either "1" or "2")

E = Value of the most recent D-echo channel bit

X<sub>1</sub> = Number of consecutive E-bits to be received as ONEs before transmitting a message of priority class 1

X<sub>2</sub> = Number of consecutive E-bits to be received as ONEs before transmitting a message of priority class 2

$X_i$  = Either  $X_1$  or  $X_2$  according to the value of "i"

Y = Binary variable indicating that the frame is pending

The SDL diagram does not cover the queuing functions which are necessary when a second DATA-REQUEST is received before the first message unit has been transmitted.

Figure 7 - SDL Presentation of the D-Channel Access Procedure

## 8.2 Activation/Deactivation

## 8.2.1 Definitions

## **8.2.1.1** Signals

The designation, the meaning and the coding of the Physical Layer signals across the S reference point are given in Table 2.

|        | Signals from the PSN to the DPE                                                                                                                                                                                                          |        | Signals from the DPE to the PSN                                                                                                                                                  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INFO 0 | Transmission of continuous binary ONEs Note 11 INFO 0 is only recognized by the DPE when it has lasted for longer than 250 μs.                                                                                                           | INFO 0 | Transmission of continuous binary ONEs Note 11 INFO 0 is not recognized by the PCSN until it has lasted for longer than 15 ms Note 12                                            |

|        |                                                                                                                                                                                                                                          | INFO 1 | A signal requesting activation, consisting of the continuous transmission of the following pattern: Positive ZERO, negative ZERO, six ONEs Nominal bit rate = 192 kbit/s Note 13 |

| INFO 2 | A signal to allow synchronization to the PCSN clock, consisting of frames with all bits of the B-, D- and D-Echo channels, set to binary ZERO, the A-bit set to ZERO, the N- and L-bits set according to the normal coding rules Note 14 |        |                                                                                                                                                                                  |

|        |                                                                                                                                                                                                                                          | INFO 3 | A signal indicating the SYNCHRONIZED or the ACTIVATED state, consisting of synchronized frames with operational data on the B- and D-channels.                                   |

| INFO 4 | A signal indicating the ACTIVATED state, consisting of frames with operational data on the B-, D-<br>and D-echo channels; the A-bit is set to ONE<br>Note 14                                                                             |        |                                                                                                                                                                                  |

Table 2 - Definition of Physical Layer Signals (Note 10)

## Note 10

With configurations where the wiring polarity may be reversed, signals may be received with the polarity of the ZEROs inverted.

#### Note 11

This value ensures that the PSN remains in the ACTIVATED state while the DPE is recovering from the LOST FRAMING state.

## Note 12

For the coding of ONEs and ZEROs see 7.5.

## **Note** 13

DPEs which do not need the capability to initiate the activation of an inactivated interface (i.e. DPEs designed to handle incoming calls only) need not have the capability to send INFO 1.

## Note 14

During transmission of INFO 2 or INFO 4, the  $F_A$  bits and the M-bits from the PT may provide the Q-bit pattern designation as described in 8.5.

## **8.2.1.2 DPE States**

The DPE states shall be as follows:

The DPE is not powered on. F1 INACTIVE

The DPE is powered on, but has not determined F2 SENSING

the type of signal, if any, that it is receiving.

The DPE is in the idle state, i.e. it is neither F3 DEACTIVATED

transmitting nor receiving a signal.

When a DPE is requested to initiate activation it F4 PENDING ACTIVATION

transmits INFO 1 and waits for a response from

the PSN.

At the first receipt of any signal from the PSN, F5 UNSYNthe DPE ceases to transmit INFO 1 and tries to **CHRONIZED**

identify signal INFO 2 or INFO 4.

F6 SYNCHRO-When the DPE receives the synchronization

signal from the PSN (INFO 2), it responds with

INFO 3, indicating that it is in the

SYNCHRONIZED state, and waits for normal

frames from the PSN (INFO 4).

This is the normal active state with the protocol F7 ACTIVATED

activated in both directions. Both the PSN and

the DPE are transmitting frames.

This is the condition when the DPE has lost **F8 LOST FRAMING**

frame alignment (see 8.3.1) and is awaiting

resynchronization by receipt of INFO 2 or INFO

4 or deactivation by receipt of INFO 0.

#### **8.2.1.3** PSN States

NIZED

The PSN states shall be as follows:

The PT is in the idle state, i.e. it is not transmit-G1 DEACTIVE

ting.

When a PT is requested to initiate activation it G2 PENDING

transmits INFO 2 and waits for a response from **ACTIVATION**

the DPE (INFO 3).

The normal active state where the PSN is trans-G3 ACTIVE

mitting INFO 4 to the DPE. The DPE to PSN di-

rection may or may no longer be active, i.e. the

PSN may deactivate or maintain the

ACTIVATED state if the DPE stops transmitting.

(The choice to deactivate is completely up to the

PSN).

G4 PENDING DEACTIVATION When the PSN wishes to deactivate it may wait for a timer (T2) to expire before returning to the DEACTIVE state.

## 8.2.1.4 Activate Primitives

The following primitives shall be used in the activate procedures:

PH-AR ACTIVATE These primitives are used to request that the MPH-AR REQUEST Physical Layer be activated.

PH-AI ACTIVATE These primitives are used by the Physical MPH-AI INDICATION Layer to indicate that it has been activated.

#### 8.2.1.5 Deactivate Primitives

The following primitives shall be used in the deactivate procedures:

MPH-DR DEACTIVATE

REQUEST

This primitive is used by the

Management Entity to request that the

Physical Layer be deactivated.

PH-DI PH-DEACTIVATE These primitives are used by the MPH-DI INDICATION Physical Layer to indicate that it has been deactivated.

## **8.2.1.6** Error and Recovery Primitives

The following primitives shall be used between the Physical Layer and the Management Entity:

MPH-EI1 MPH-ERROR MPH-EI1 indicates an error report. The message unit contains the type of the error. This can be: receiving INFO 2 instead of INFO 4;

loss of framing.

MPH-EI2 MPH-ERROR MPH-EI2 reports that no error condition now INDICATION 2 exists.

MPH-EI3 MPH-ERROR MPH-EI3 indicates that the E-bit received was not equal to the corresponding D-bit.

Optional parameters may convey additional information, see 9.4.

#### 8.2.1.7 Connection/Disconnection Primitives

The following primitives shall be used between the Physical Layer and the Management Entity:

MPH-II MPH-Information INDICATION

(c) MPH-II (c) indicates that the Physical Layer is in the "connected" status.

(d)

MPH-II (d) indicates that the Physical Layer is in the "disconnected" status.

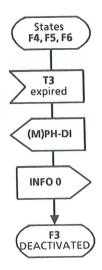

## **8.2.1.8** Primitive Sequences

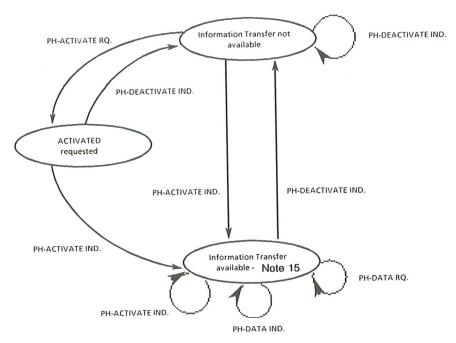

The primitives defined in 8.2.1.4 to 8.2.1.6 specify, conceptually, the service provided by the Physical Layer to the Data Link Layer and to the Physical Layer Management entity. The constraints on the sequence in which the primitives may occur are specified in Figure 8 and 9. The diagrams do not represent states which must exist for the Physical Layer entity. However, they do illustrate the condition that the Data Link Layer and the Management entities perceive the Physical Layer to be in as a result of the primitives transferred between the entities. Furthermore, the Figures do not represent an interface and are used for modelling purposes only.

Figure 8 - Primitive Interchange between the Physical Layer and the Data Link Layer

#### Note 15

The Data Link Layer will not be aware if the information transfer capability is temporarily interrupted.

## 8.2.2 Activation/Deactivation Procedure at the Terminal Side

When a locally powered DPE is able to detect power source 1, it shall transmit INFO 0, when it is first connected and senses power source 1, or upon the loss of frame alignment, see 8.3.

Figure 9 - Primitive Interchange between the Physical Layer and the Management Entity (DPE Side)

## Note 16

The use of MPH-ACTIVATE-REQ for maintenance purposes is for future standardization.

When the DPE has achieved frame alignment, it shall transmit INFO 3. The satisfactory transmission of operational data cannot be assured prior to the receipt of INFO 4. Procedures are shown in Table 3.

A DPE which determines that it is connected to a PT not providing power source 1 shall default to the procedures described in Table 4.

|                                    | INACTIVE  |                | CENCING                               | DEACTI-                                 | AVAITING                                | IDENTI-<br>FYING                        | SYNCHRO-                                | ACTI-                                   | LOST                                   |

|------------------------------------|-----------|----------------|---------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|----------------------------------------|

| STATE NAME                         | Power off | Power<br>on    | SENSING                               | VATED                                   | SIGNAL                                  | INPUT                                   | NIZED                                   | VATED                                   | FRAMING                                |

| State Number                       | F1.0      | F1.1           | F2                                    | F3                                      | F4                                      | F5                                      | F6                                      | F7                                      | F8                                     |

| Info sent                          | INFO 0    | INFO 0         | INFO 0                                | INFO 0                                  | INFO 1                                  | INFO 0                                  | INFO 3                                  | INFO 3                                  | INFO 0                                 |

| Loss of power<br>Note 18           | /         | F1.0           | F1.0                                  | MPH-EII(d)<br>MPH-DI,<br>PN-DI;<br>F1.0 | MPH-EII(d)<br>MPH-DI,<br>PN-DI;<br>F1.0 | MPH-EII(d)<br>MPH-DI,<br>PN-DI;<br>F1.0 | MPH-EII(d)<br>MPH-DI,<br>PN-DI;<br>F1.0 | MPH-EII(d)<br>MPH-DI,<br>PN-DI;<br>F1.0 | PH-EII(d)<br>MPH-DI,<br>PN-DI;<br>F1.0 |

| App. of power<br>Note 18           | F1.1      | 1              | 1                                     | 1                                       | 1                                       | 1                                       | 1                                       | 1                                       | 1                                      |

| Detect Power S                     | /         | MPH-EI2<br>GI2 | 1                                     | 1                                       | /                                       | 1                                       | 1                                       | 1                                       | /                                      |

| Disapp. Power S                    | 1         | /              | F1.1                                  | MPH-EII(d)<br>MPH-DI,<br>PN-DI;<br>F1.1 | MPH-EII(d)<br>MPH-DI,<br>PN-DI;<br>F1.1 | MPH-EII(d)<br>MPH-DI,<br>PN-DI;<br>F1.1 | MPH-EII(d)<br>MPH-DI,<br>PN-DI;<br>F1.1 | MPH-EII(d)<br>MPH-DI,<br>PN-DI;<br>F1.1 | PH-EII(d)<br>MPH-DI,<br>PN-DI;<br>F1.1 |

| (M)PH-Activate<br>Request          | 1         | I              | I                                     | ST. T3<br>F4<br>Note 19                 | 1                                       | I                                       | -                                       | (М)РН-АІ                                | -                                      |

| Expiry T3                          | 1         | /              | _                                     | _                                       | (M)PH-DI;<br>PN-DI;<br>F3               | (M)PH-DI;<br>PN-DI;<br>F3               | (M)PH-DI;<br>PN-DI;<br>F3               | -                                       | -                                      |

| Receiving INFO<br>0                | 1         | /              | MPH-II(c);<br>F3                      | -                                       | -                                       | -                                       | MPH-DI;<br>PH-DI;<br>F3                 | MPH-DI;<br>PH-DI;<br>F3                 | MPH-DI;<br>PH-DI;<br>MPH-EI2<br>F3     |

| Receiving any<br>signal<br>Note 17 | 1         | /              | -                                     | _                                       | F5                                      | -                                       | /                                       | /                                       | _                                      |

| Receiving INFO<br>2                | 1         | /              | MPH-II(c);<br>F6                      | F6                                      | /                                       | F6                                      |                                         | MPH-EI1;<br>F6                          | MPH-EI2;<br>F6                         |

| Receiving INFO<br>4                | /         | /              | MPH-II(c);<br>PH-AI;<br>MPH-AI;<br>F7 | PH-AI;<br>MPH-AI;<br>F7                 | /                                       | PH-AI;<br>MPH-AI;<br>F7                 | PH-AI;<br>MPH-AI;<br>MPH-EI2;<br>F7     | -                                       | PH-AI;<br>MPH-AI;<br>MPH-EI2;<br>F7    |

| Lost Framing                       | /         | /              | 1                                     | /                                       | /                                       | /                                       | MPH-EI1;<br>F8                          | MPH-EI1;<br>F8                          | _                                      |

Legend: Impossible due to the definition of the Physical Layer service

No Change

Impossible Situation

P;Fn means: "Issue primitive P and then go to state Fn"

Primitives: The indexes "(c)" and "(d)" indicate "connected" and "disconnected", respectively.

Table 3 - Activation/Deactivation for locally powered DPEs, able to detect Power Source 1

(Use confined to PTs which provide power source 1)

## Note 17

This event reflects the case where some signal is received and the DPE has not (yet) determined whether it is INFO 2 or INFO 4.

## Note 18

The term "power" may designate full operational or backup power. Backup power is defined to provide enough energy to hold the TEI value in memory and to maintain the capability of receiving and transmitting the Data Link Layer frames associated with the TEI assignment procedure.

## Note 19

Timer T3 may be implemented in the Physical Layer or elsewhere.

A functional SDL description of the procedure is presented in 8.2.5.

Locally powered DPEs shall, when power is removed, initiate the transmission of INFO 0 before frame alignment is lost.

## 8.2.3 Activation/Deactivation Procedure at the PSN Side

This procedure is beyond the scope of this Standard. For the provision of background information, however, it is shown in Table 4 in the form of a finite state matrix. A functional SDL description of the procedure is presented in 8.2.4.

| STATE NAME                         | INACTIVE | SENSING                               | DEACTI-<br>VATED          | AVAITING<br>SIGNAL                   | IDENTI-<br>FYING<br>INPUT            | SYNCHRO-<br>NIZED                    | ACTI-<br>VATED                       | LOST<br>FRAMING                      |

|------------------------------------|----------|---------------------------------------|---------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|

| State Number                       | F1.0     | F2                                    | F3                        | F4                                   | F5                                   | F6                                   | F7                                   | F8                                   |

| Info sent                          | INFO 0   | INFO 0                                | INFO 0                    | INFO 1                               | INFO 0                               | INFO 3                               | INFO 3                               | INFO 0                               |

| Loss of power<br>Note 21           | /        | F1                                    | MPH-II(d)<br>F1           | MPH-II(d)<br>MPH-DI,<br>PH-DI;<br>F1 | MPH-II(d)<br>MPH-DI,<br>PH-DI;<br>F1 | MPH-II(d)<br>MPH-DI,<br>PH-DI;<br>F1 | MPH-II(d)<br>MPH-DI,<br>PH-DI;<br>F1 | MPH-II(d)<br>MPH-DI,<br>PH-DI;<br>F1 |

| App. of power<br>Note 21           | F2       | 1                                     | 1                         | /                                    | /                                    | 1                                    | 1                                    | 1                                    |

| Detect Pwr S. 1                    | 1        | /                                     | 1                         | 1                                    | 1                                    | /                                    | 1                                    | /                                    |

| Disapp. Pwr S. 1                   | 1        | 1                                     | 1                         | 1                                    | 1                                    | 1                                    | 1                                    |                                      |

| (M)PH-Activate<br>Request          | 1        | I                                     | Start T3<br>F4<br>Note 22 | 1                                    |                                      | -                                    | (М)РН-АІ                             | -                                    |

| Expiry T3                          | /        | /                                     | _                         | MPH-DI;<br>PN-DI;<br>F3              | MPH-DI;<br>PN-DI;<br>F3              | MPH-DI;<br>PN-DI;<br>F3              | -                                    | -                                    |

| Receiving INFO 0                   | /        | MPH-II(c);<br>F3                      | -                         | -                                    | _                                    | MPH-DI;<br>PH-DI;<br>F3              | MPH-DI;<br>PH-DI;<br>F3              | MPH-DI;<br>PH-DI;<br>MPH-EI2<br>F3   |

| Receiving any<br>signal<br>Note 20 | /        | -                                     | -                         | F5                                   | -                                    | /                                    | /                                    |                                      |

| Receiving INFO 2                   | 1        | MPH-II(c);<br>F6                      | F6                        | 1                                    | F6                                   | -                                    | MPH-EI1;<br>F6                       | MPH-EI2;<br>F6                       |

| Receiving INFO 4                   | /        | MPH-II(c);<br>PH-AI;<br>MPH-AI;<br>F7 | PH-AI;<br>MPH-AI;<br>F7   | /                                    | PH-AI;<br>MPH-AI;<br>F7              | PH-AI;<br>M;PH-AI;<br>MPH-EI2;<br>F7 | -                                    | PH-AI;<br>M;PH-AI;<br>MPH-EI2;<br>F7 |

| Lost Framing                       | 1        | 1                                     | 1                         | 1                                    | 1                                    | MPH-EI1;<br>F8                       | MPH-EI1;<br>F8                       | -                                    |

Legend:

Impossible due to the definition of the Physical Layer service

No Change

/ Impossible Situation

P;Fn means: "Issue primitive P and then go to state Fn"

Primitives:

The indexes "(c)" and "(d)" indicate "connected" and "disconnected", respectively.

Table 4 - Activation/Deactivation for DPEs locally powered, not able to detect Power Source 1

#### Note 20

This event reflects the case where some signal is received and the DPE has not (yet) determined whether it is INFO 2 or INFO 4.

## Note 21

The term "power" may designate full operational or backup power. Backup power is defined to provide enough energy to hold the TEI value in memory and to maintain the capability of receiving and transmitting the Data Link Layer frames associated with the TEI assignment procedure.

## Note 22

Timer T3 may be implemented in the Physical Layer or elsewhere.

| STATE NAME                    | DEACTIVE<br>(Note 4) | PENDING<br>ACTIVATION                          | ACTIVE                            | PENDING<br>DEACTIVATION<br>(Note 4) |  |

|-------------------------------|----------------------|------------------------------------------------|-----------------------------------|-------------------------------------|--|

| State Number                  | G1                   | G2                                             | G3                                | G4                                  |  |

| Info sent                     | INFO 0               | INFO 2                                         | INFO 4                            | INFO 0                              |  |

| (M)PH-Activate Request        | set T1 Note 23<br>G2 | /                                              | (M)PH-AI                          | set T1 Note 23<br>G2                |  |

| (M)PH-Deactivate<br>Request   | MPH-DI               | set T2 Note 24<br>(M)PH-DI;<br>G4              | set T2 Note 24<br>(M)PH-DI;<br>G4 | -                                   |  |

| Expiry of Timer T1<br>Note 23 | -                    | set T2 Note 24<br>(M)PH-DI;<br>G4              | (M)PH-DI; /                       |                                     |  |

| Expiry of Timer T2<br>Note 24 | -                    | -                                              | -                                 | G1                                  |  |

| Receiving INFO 0              | -                    | -                                              | (M)PH-DI;<br>(M)PH-EI;<br>G2      | G1                                  |  |

| Receiving INFO 1              | set T1 Note 23<br>G2 | -                                              | /                                 | -                                   |  |

| Receiving INFO 3              | /                    | set T1   Note 23<br>(M)PH-AI;<br>G3<br>Note 25 | -                                 | -                                   |  |

| Loss of framing               | 1                    | 1                                              | (M)PH-DI;<br>(M)PH-EI;<br>G2      | -                                   |  |

Legend:

No Change

/ Impossible Situation

P;Gn means: "Issue primitive P and then go to state Gn"

Table 5 - Activation/Deactivation of the Physical Layer at the PSN Side

## Note 23

12;

Timer T1 is a supervisory timer which has to take into account the overall time to activate.

## Note 24

Timer T2 prevents unintentional reactivation. Its value is between 25 ms and 100 ms. This implies that a DPE has to recognize INFO 0 and to react on it within 25 ms. If the PSN is able to unambiguously recognize INFO 1, then the value of timer T2 may be 0.

#### Note 25

As an option, the primitive and INFO 4 may be send only 100 ms, after INFO 3 has been received.

#### Note 26

Some PTs may never deactivate. In this case, they never enter states G1 nor G4, and timers T1 and T2 do not exist.

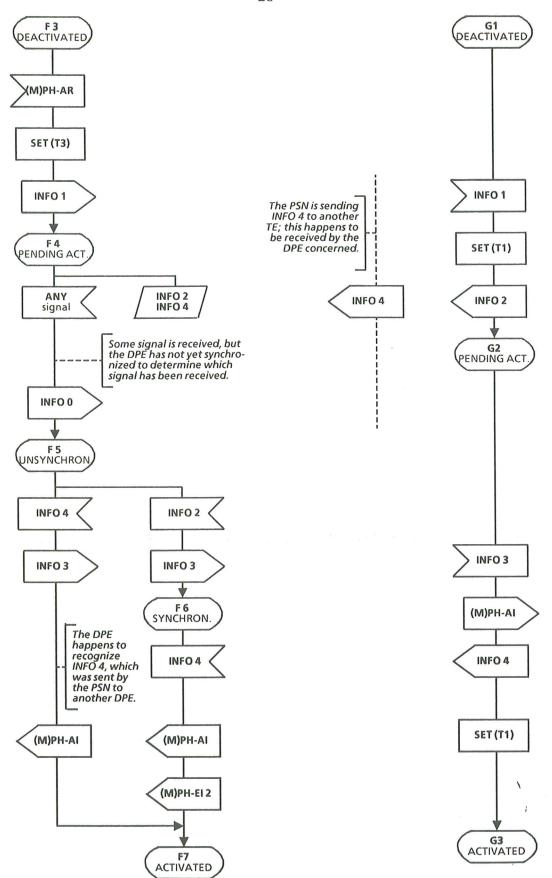

## 8.2.4 SDL Presentation of the Activation/Deactivation Procedure

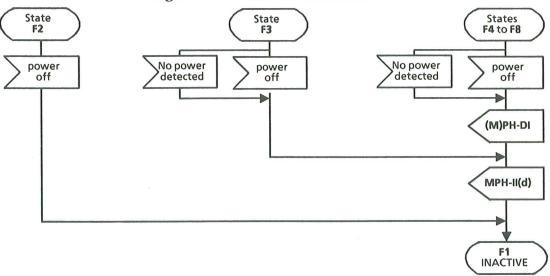

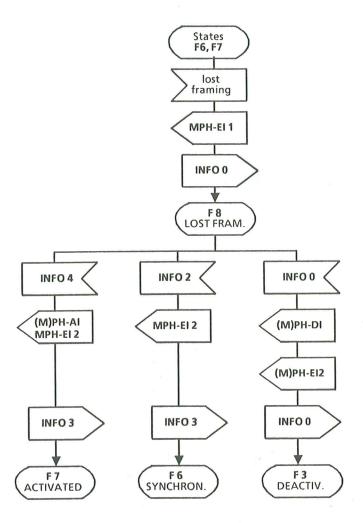

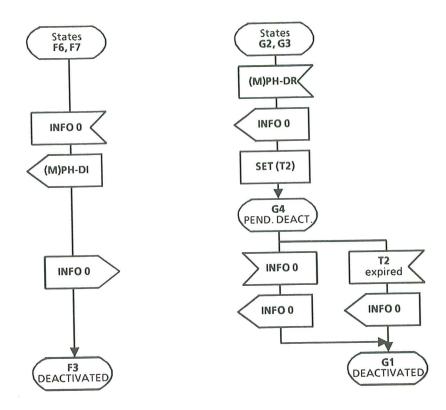

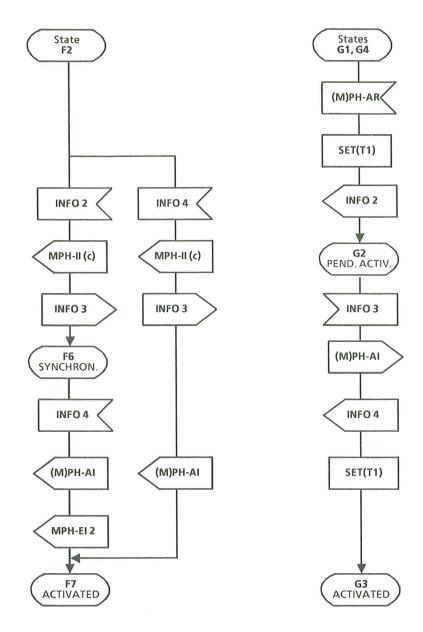

Figures 10 to 19 show the interworking between the DPE and (as far as applicable and necessary for understanding) the PSN side of the Physical Layer Activation/Deactivation protocol. The protocol is partitioned as follows:

Transition from the POWER-OFF to the DEACTIVATED state The DPE is forced to re-enter the SYNCHRONIZED state

Activation initiated by the DPE

Activation Failure at the DPE side

Status Verification

The DPE has lost Framing

The DPE has lost Power

The PSN releases the Physical Layer Connection

Activation initiated by the PSN

The activation/deactivation signals are continuous signals. An (external) output symbol indicates that the transmission of such continuous signal is to be started. The transmission of this signal ends when it is replaced by another signal to be sent in the same direction. An (external) input symbol indicates that an incoming signal has arrived.

The SDL symboling used assumes that the DPE is on the left and the PSN is on the right hand side of a functional interworking model as depicted in Figure 10.

Figure 10 - Functional Interworking Model

There is no corresponding sequence at the PSN side of the S<sub>0</sub> interface.

Figure 11 - Transition from the INACTIVE to the DEACTIVATED State

The corresponding sequence at the PSN side of the S<sub>0</sub> interface is out of the scope of this Standard.

Figure 12 - The DPE is forced to re-enter the SYNCHRONIZED State

Figure 13 - Activation initiated by the DPE

Figure 14 - Activation Failure at the DPE Side

Figure 15 - Status Verification

Figure 16 - The DPE has lost Power or does not detect Power at the Interface

Note 27

Only relevant, if the DPE monitors power at the  $S_0$  interface.

Figure 17 - The DPE has lost Framing

Figure 18 - The PSN Releases the Physical Layer Connection

Figure 19 - Activation initiated by the PSN

# 8.2.5 Timing Values

### 8.2.5.1 Timers

The expiry of timers is used to select an alternative sequence in order to continue and conclude the procedure in an orderly fashion even when an expected reaction fails.

Three timers shall be used in the Physical Layer protocol:

PSN side Timer T1 supervises whether or not the Physical Layer

can be activated by the PSN. The specification of its

value is outside the scope of this Standard.

Timer T2 gives the TEs sufficient time to recognize INFO 0 and to enter the DEACTIVATED state. According to CCITT Rec. I.430, its value is specified as

25 ms to 100 ms.

DPE side Timer T3 gives the PSN sufficient time to recognize

INFO 1 and to respond by transmitting INFO 2. The

value of T3 shall be 3 s.

If the PSN fails to respond before T3 expires, a reattempt may be initiated by higher layers or the Manage-

ment Entity.

## 8.2.5.2 Reaction Times of the DPE

In the SYNCHRONIZED state the DPE shall recognize the receipt of INFO 4 within two frames (in the absence of errors).

The DPE shall send INFO 3 within 100 ms of receipt of INFO 2 or INFO 4.

In accordance with CCITT Rec. I.430, the DPE shall react on INFO 0 within 25 ms.

# 8.3 Frame Alignment Procedures

The first bit of each frame shall be the framing bit F; it shall be a ZERO.

The frame alignment procedures makes use of the fact that the framing bit is represented by a pulse having the same polarity as the preceding pulse which is a violation of the alternate mark inversion (AMI) scheme; this intentional violation is used for reframing.

To guarantee secure framing the auxiliary framing bit pair  $F_A$  and N in the direction PT to DPE or the auxiliary framing bit  $F_A$  with the associated balancing bit L in the direction DPE to PT are introduced. For the direction PT to DPE, this ensures that there is always an AMI violation at 14-bits or less (the 14-bit criterion) from the framing bit F, due to  $F_A$  or N being a ZERO. For the direction DPE to PT, it ensures that there is always an AMI violation at 13-bits or less (the 13-bit criterion), due to  $F_A$  being always ZERO. The framing procedures do not depend on the polarity of the framing bit F and thus are not sensitive to wiring polarity.

The coding rule for the auxiliary framing bit pair  $F_A$  and N in the direction PT to DPE is such that N is the binary opposite of  $F_A$ , i.e.:

The  $F_A$  and L bit in the direction DPE to PT are always coded such that the binary values of  $F_A$  and L are equal.

## 8.3.1 Frame Alignment Procedure in the Direction PT to DPE

Frame alignment on initial activation of the DPE shall comply with the timing value defined in 8.2.6.2.

- **8.3.1.1** Loss of frame alignment shall be assumed when a time period equivalent to two 48-bit frames has elapsed without having detected valid pairs of AMI violations, obeying the 14-bit criterion as described above. The DPE shall cease transmission immediately.

- **8.3.1.2** Frame realignment shall be assumed to occur when 3 consecutive pairs of line AMI violations, obeying the 14-bit criterion, have been detected.

## 8.3.2 Frame Alignment in the Direction DPE to PT

The 13-bit criterion shall apply.

- **8.3.2.1** The PT may assume loss of frame alignment if a time period equivalent to two 48-bit frames has elapsed since detecting consecutive violations according to the 13-bit criterion. On detection of loss of framing, the PT shall either continue transmitting towards the DPE (i.e. remain in the ACTIVATED state) or initiate deactivation by transmitting INFO 0 (i.e. take the PENDING DEACTIVATION state).

- **8.3.2.2** The PT may assume that frame alignment has been regained when 3 consecutive pairs of AMI violations, obeying the 13-bit criterion, have been detected.

### 8.4 Idle Channel Code on B-Channels

A DPE shall send ONEs in any B-channel which is not assigned to it. This is the responsibility of higher layers.

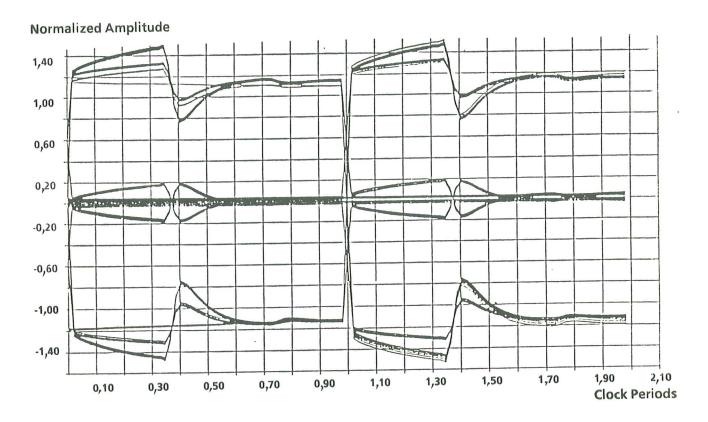

### 8.5 Multiframing